ロードマップでわかる!当世プロセッサー事情 第727回

6月11日から京都で開催されていた2023 Symposium on VLSI Technology and Circuitにおいて、インテルは基板裏面から電源を供給する配線方式「PowerVia」関連の内容を2つ発表した。

1つはT1-1の“E-Core implementation in Intel 4 with PowerVia(Backside Power) Technology”、もう1つがT6-1の“Intel PowerVia Technology: Backside Power Delivery for High Density and High-Performance Computing”である。どちらも似てはいるのだが、後者がPowerVia全体の発表で、前者はこれをIntel 4プロセスに移植した上で、E-coreに実装してみた結果を示したものである。

実はこの件に関しては事前説明会もあったのだが、ちょうどCOMPUTEXやAMDの新製品の話などと見事に時期が被った関係で、少し遅くなったが今回まとめて説明しよう。

基板裏面から電源を供給する配線方式

PowerVia

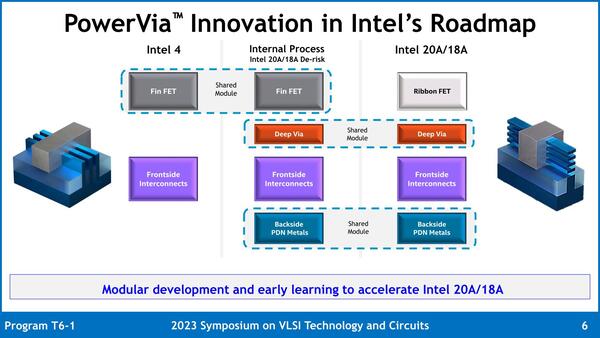

PowerViaの概略は連載656回で紹介した。要するにトランジスタ層の裏側から電源供給をする方式である。このPowerVia、本来はIntel 20Aで導入される技術でありそれは今回も変わっていないのだが、いきなりIntel 20Aに導入するのではなく、まず先行してIntel 4に試験的に実装してみた、というのが今回の発表である。

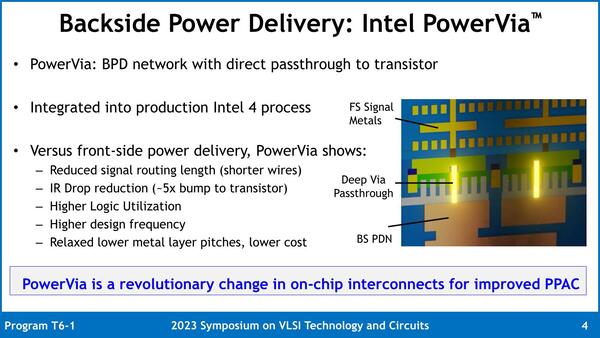

そもそもPowerViaというか、一般にはBackside Power Deliveryという呼び方をするが、この目的はなにか? というのを1枚にまとめたのが下の画像だ。

配線層に電源ラインを通す必要がなくなるので、複雑化している配線層の混雑を緩和でき、これは配線遅延の軽減などに貢献する。また電源配線をより太くすることが可能なので、配線抵抗にともなう電圧低下などの軽減も可能であり、これは長い目で見ればロジック回路の効率化や動作周波数の向上などの効果も得られる。

上の画像の右のイラストで黄色と緑色の部分がトランジスタ層、その上にある金色の部分がFS(Front Side)の信号配線であり、トランジスタ層の下の大きな金色の部分がBS PDN(Back Side Power Delivery Network)というわけだ。ちなみにこれはイメージ図であって、実際の断面図ではない。

余談だがこのBackside Power Deliveryに関しては、今回インテルだけでなくimecやSamsungなども発表しており、特にimecは発表に加えて短期講座やワークショップでもこれを取り上げているあたりは、けっこう旬な技術という感じになっている。

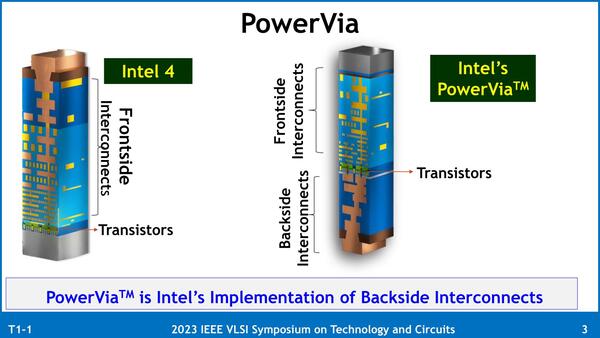

下のイメージ図は以前も公開されていたもので、やはりコンセプト図に近いが、上の画像よりはわかりやすいかもしれない。従来は配線層の上にPDNがあったのが、全部トランジスタ層の裏に移動した格好だ。これにより配線層がだいぶすっきりしたのが見て取れる。

そのPowerViaを今回Intel 4に移植したのは、要するにリスクを減らすためである。そうでなくてもIntel 20A/18AはRibbon FETという名称のGAA構造で、これだけでも十分チャレンジである。そこに加えてPowerViaまで同時に実装するのはやはりリスクが高い、と判断したのは妥当だろう。

からの記事と詳細 ( CPU革命! 裏面電源供給技術PowerViaのテスト実装に成功 インテル CPUロードマップ (1/3) - ASCII.jp )

https://ift.tt/90VGyEh

No comments:

Post a Comment